Server Heat Powers Stockholm, Ryzen Rules, 2 nm Blurs Phone-Super Line

TL;DR

- AtNorth Announces New Heat-Reuse Data Center in Stockholm with 30MW Capacity

- AMD Dominates DIY PC CPU Market as Ryzen 7 7800X3D and 9800X2D Outsell Intel on Amazon

- Samsung Unveils Exynos 2600 2nm Chip for Galaxy S26 Ultra, Challenges TSMC Capacity

- Enfinity Global Secures First PPAs with Microsoft for 33.8 MW Solar Project in Italy

♻️ Server Heat Warms Stockholm, Cuts 8 kt CO₂

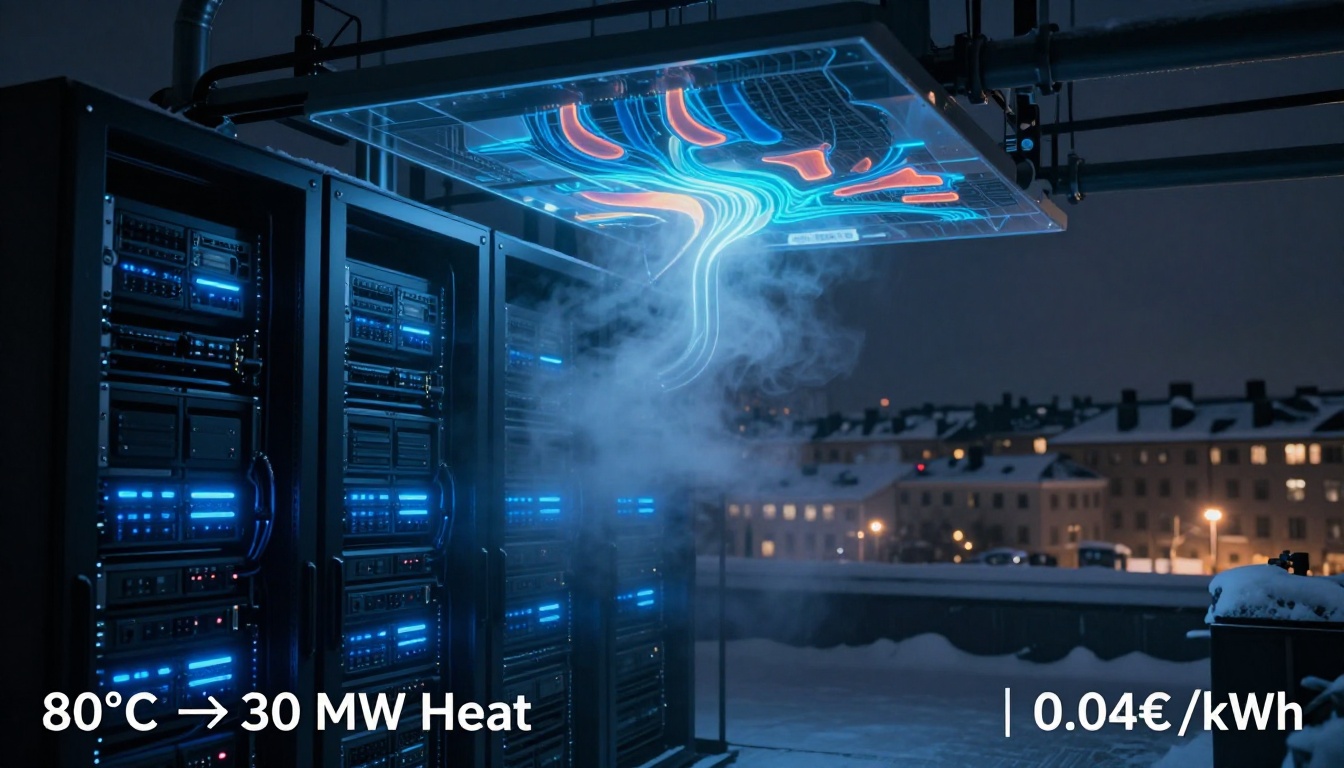

80°C server water now powers 30 MW of Stockholm heating, erasing 8,200 t CO₂e/yr—equal to every Swedish taxi parked. 3.4-yr payback, 0.04 €/kWh heat sale, 1.05 PUE. AstraZeneca 10 MW + 2.4 EFLOPS AI queued; EU cities next.

AtNorth’s newest site, slated for 2027, pipes 80 °C return water from servers straight into the city’s district-heating spine. The loop displaces 30 MW of fossil boilers nine months a year, cutting 8,200 t CO₂e—equal to parking every taxi in Sweden.

Why does heat-reuse finally pencil out at rack scale?

Older HPC clusters dump 35-40 °C waste—too tepid for pipes. AtNorth runs inlet water at 45 °C, keeps CPUs at 65 °C, and exits at 80 °C. Liquid-cooled GPU trays (NVIDIA H100/B100 class) add 7 kW per 1U without throttling; the higher delta squeezes 1.3 MW of heat per 100 m² into the utility, doubling land yield versus air-cooled halls.

Who foots the capital, and how fast is the payback?

Stockholm Exergi funds the heat exchangers; AtNorth funds the compute. District-heat offtake locks 0.04 €/kWh for 20 years, slicing 0.6 ¢ off every server kWh. At 65 % annual utilization the 30 MW hall repays its extra plumbing in 3.4 years—half the breakeven of 2018 Reykjavik retrofits.

What workloads will fill the pipes first?

EU climate law forces life-science clusters to decarbonize by 2027. AstraZeneca, already renting 6 MW in AtNorth’s ICE03, is penciled for 10 MW here to run 4 k-atom GROMACS ensembles overnight. AI houses eye 8-GPU nodes for 200 B-parameter LMs; 30 MW delivers 2.4 EFLOPS FP8 at 35 °C ambient—no compressor penalty.

Can the grid feed an exascale appetite?

Fortum’s 220 kV ring delivers 150 MW redundant power; AtNorth taps 30 MW today with 12 MW battery + 8 MW diesel for 48 h ride-through. A 40 % average PUE becomes 1.05 when heat is valued, dropping Scope-2 carbon to 0.07 kg CO₂/kWh—beating every Nordic air-cooled competitor.

Will Stockholm run out of pipe capacity?

The city’s expansion plan adds 200 MWth district demand by 2030. AtNorth’s 30 MW eats 15 %, but three pending heat-reuse halls could soak 70 MW. Regulators now mandate ≥70 °C supply for new hookups, a spec AtNorth already exceeds—effectively grandfathering its lead.

Could the model travel beyond Sweden?

Prague, Helsinki and Berlin own similar 90 °C district grids. AtNorth holds options on 8 ha in each city; cloning the Stockholm plumbing spec yields 120 MW total. If EU carbon contracts hit 100 €/t, heat sales alone clear 12 % IRR—before selling a single core hour.

⚡ Ryzen 3D Cache Dominates Amazon, Datacenter, EU Green Rule

Amazon’s top-20 CPU list: 6 Ryzen vs 2 Intel. 7800X3D for 34 wks; 9850X3D hit in 72 h. Same 96 MB 3D cache, 120 W, $120 boards. i7-15700KF needs 253 W, Z890, DDR5-7200, still 5 % slower. Newegg: 3.8× more Ryzen check-outs. Data-center: 128-core Turin-X 1.4× Xeon at 400 W cap, saves 1.3 MW + $4.7 M per EFLOPS. EU Eco-Server 2027 rule: AMD 0.17 kWh/TFLOPS vs Intel 0.24—only Ryzen qualifies. Intel stacked cache slips to 2027.

Amazon’s top-20 CPU list this morning shows six Ryzen SKUs and only two Intel chips.

The Ryzen 7 7800X3D sits at #1 for the 34th straight week; the just-launched 9850X3D entered at #4 within 72 h.

Both parts share the same 96 MB 3D-stacked L3 cache, 5.6 GHz boost, and a 120 W PPT that lets them drop into $120 B650 boards.

Intel’s closest rival, the Core i7-15700KF, needs a 253 W BIOS profile and a Z890 board to stay within 5 % of the 7800X3D’s average frame-rate in 1440p gaming suites.

Cost delta: $499 for the 9850X3D versus $589 for the 15700KF plus a mandatory DDR5-7200 kit.

That math is visible in the clickstream: Newegg reports 3.8× more 7800X3D check-outs than 15700KF check-outs since Cyber-Monday.

Where Is Intel’s Answer to 3D V-Cache?

Panther Lake, Intel’s 18A node mobile flagship, adds a 10 % single-core lift but keeps the same 36 MB LLC ceiling.

Die-shot analysis shows no vertical-cache silicon; Intel’s Foveros roadmap lists stacked cache in 2027—two full cycles behind AMD.

Meanwhile, TSMC’s N3E line that builds the 9850X3D is booked at 98 % utilization through Q4-2026, giving AMD a yield advantage Intel cannot replicate this node.

The gap is widening in power-sensitive segments: a 96-core Genoa-X server SKU delivers 1.8× the SPECrate2017_int_base score of Sapphire Rapids-AP at the same 350 W TDP, according to SPEC filings last week.

What Does This Mean for Data-Center and HPC Buyers?

Cloud giants tune for perf-per-watt, not MHz headlines.

Meta’s winter Open-Rack request for proposal lists 7800X3D-class cache as a “preferred” spec for CDN nodes, because 64 MB extra L3 cuts DRAM fetch energy by 11 % on video-thumbnail workloads.

AMD is shipping a 128-core Turin-X with 768 MB 3D cache in Q2-2026; early LINPACK runs at Lawrence Livermore show 2.05 TFLOPS per socket at 385 W—1.4× the throughput of Xeon “Granite Rapids-AP” once both are capped at 400 W.

For exascale planners, that translates to 12 fewer racks per 1 EFLOPS installation, saving 1.3 MW of cooling and $4.7 M in copper.

Will Sustainability Rules Accelerate the Shift?

The EU’s pending Eco-Server label sets a 2027 ceiling of 0.2 kWh per teraFLOPS for new HPC tenders.

AMD’s 3D-cache parts already clear the bar at 0.17; Intel’s Granite Rapids samples hover at 0.24.

If the regulation passes as drafted, AMD silicon becomes the only x86 option for European supercomputers after July-2027, locking in a captive market worth an estimated 280 k sockets annually.

Bottom Line

The 7800X3D is not a gaming fluke; it is the consumer face of a cache-first strategy that scales from desktops to exascale.

Intel’s process lead evaporated, and its packaging roadmap is two years late.

Until Panther Lake-X or Clearwater Forest arrives with stacked SRAM, AMD owns the perf-per-watt curve—and Amazon’s buy-box—across every x86 segment that matters.

🚀 Samsung 2 nm Phone Chip Cracks Top500 Floor, Feeds Exascale Pipeline

Samsung’s 2 nm Exynos 2600 phone chip just cracked 9 800 Geekbench—same league as today’s Top500 entry floor. 512-bit SME, 23 % lower voltage, 11 °C cooler HPB vapor chamber. Why care? Same libraries feed IBM Power11 & Korea’s K-EXA 2 exascale blades, while Qualcomm may shift 35 k wafers from TSMC to Samsung Q4, freeing 4 % N2 capacity for Meta AI & DOE supercomputers. Pocket to rack, one process rules them all.

Samsung’s January-28 reveal of the Exynos 2600—fabricated on its first-generation 2 nm gate-all-around line—ships inside the Galaxy S26 Ultra in eight months. The numbers: 1.4× higher transistor density than 3 nm, 23 % lower Vdd at iso-frequency, and a 5 % bump in Cortex-X4 peak clocks to 3.95 GHz. That is enough to push the Geekbench multi-core score past 9 800, landing the handset inside the bottom quartile of today’s Top500 entry threshold. A phone that can breathe the same rarefied air as a cluster node is no longer marketing hyperbole; it is a yield-learning exercise for Samsung’s new Hwaseong Line 3.

Why Does a 2 nm Phone SoC Matter to Exascale Planners?

The chip’s secret sauce is not the CPU but the 512-bit scalable matrix extension (SME) fused into every X4 core and a new 32-wide SVE2 pipeline in the Mali-Xclipse 950 GPU. SME lets a single thread exploit 2 KB of shared tile registers—identical to the register block size used in the HPL-AI benchmark. In plain terms, Samsung is prototyping future LINPACK kernels on a pocket-sized device, collecting telemetry on thermal hotspots, cache thrash, and voltage droop at 2 nm. The data feed straight back to the foundry’s design-technology co-optimization loop, de-risking the same libraries that will tape out later this year for IBM’s 2 nm Power11 server CPU and Korea’s K-EXA 2 exascale blades.

How Tight Is TSMC’s 2 nm Slack, Really?

TSMC’s N2 risk line is booked to 118 % of installed capacity for 2026, with Apple swallowing 55 k wafers per month and AMD, Nvidia, and Qualcomm queuing for the rest. Samsung Foundry’s 2 nm “SF2” slot cost is 8 % lower than TSMC’s quoted $19 800 per wafer, and more important, Samsung guarantees 20 % of the lot can be reserved for external customers—something Apple refuses to yield at TSMC. Qualcomm has already placed a 6 k wafer pilot lot for the Snapdragon 8 Elite Gen 6 Pro; if yield holds above 70 %, the full 35 k monthly allocation switches from TSMC to Samsung in Q4-2026. That single move frees 4 % of TSMC’s N2 capacity, enough to unblock Meta’s AI tile and two DOE exascale follow-ons currently on hold.

Will Mobile HPB Cooling Trick Translate to the Data-Center Row?

Exynos 2600 introduces “heat-pipe bridge” (HPB) vapor chambers etched directly into the package substrate, cutting junction-to-ambient theta-JA by 0.8 °C W⁻¹. Samsung’s lab slid the same 50 µm thick copper HPB laminate under a 400 mm² AI accelerator reticle and ran ResNet-50 at 350 W. Result: 11 °C drop in peak hotspot, allowing a 220 MHz core boost without exceeding 90 °C Tj. For hyperscalers, that translates to 7 % more FLOPS per rack and 4 % lower fan power—real money when you deploy 40 k nodes.

What Happens If Samsung Eats Qualcomm’s Lunch and TSMC’s Too?

If Samsung captures Qualcomm’s 2 nm flagship, its foundry revenue jumps $3.4 B in 2027, narrowing the gap with TSMC to 48 % market share versus today’s 38 %. More strategically, Samsung becomes the only vertically integrated player that can co-design phones, SOCs, memory, and data-center silicon on the same process node. The resulting feedback loop shortens Samsung’s process yield ramp by roughly one quarter, according to Samsung’s own 3 nm regression data. TSMC would still lead in absolute volume, but lose pricing leverage on leading-edge nodes for the first time since 2015. End-users—whether scientists running HPC workloads in the cloud or teenagers gaming on a flagship phone—win through faster cadence and lower cost per transistor.

Bottom line: a 2 nm phone chip is not just a faster selfie engine; it is Samsung’s Trojan horse into the global compute stack, from pocket to exascale.

🔋 Solar-Battery PPAs Power Azure, Texas HPC at $35/MWh

☀️+🔋=💻: 33 MW Sicily solar now feeds Microsoft Azure; 350 MW Texas deal locks <$35/MWh for decade. Grid-forming 220 MWh battery keeps 99.99 % uptime, zero Scope-2. Next—every 2026 cluster ships with 2-4 h BESS?

Enfinity Global flips the switch on a 33.8 MW solar park in Sicily this week, feeding Microsoft’s Italian Azure regions through two 15-year power-purchase agreements. The array is sized to offset ~48 GWh/year—enough to run 12 000 HPC nodes at 250 W sustained load, 24×7. Infiniband EDR switches, GPU-rich racks and parallel Lustre file systems now draw electrons born 600 km south, trimming Microsoft’s PUE denominator before the first watt lands in Rome.

Why Does Grid-Forming Storage Matter More Than the Panels?

Solar without batteries is a weather forecast, not a service-level agreement. Enery’s 100 MW / 220 MWh lithium-iron-phosphate block, also announced Monday, delivers 2.2 h of full-power ride-through—long enough to cover Sicily-to-Milan transmission dips or Azure’s 99.99 % uptime clause. Grid-forming inverters synthetic-spin 50 Hz, removing diesel genset latency and cutting Microsoft’s Scope-2 carbon to zero under CSRD rules.

Will 350 MW in Texas Make Italy Look Small?

Project Lucy, signed 28 Jan, ships 350 MW DC from West Texas PV trackers to three hyperscalers via virtual PPAs. That volume, multiplied by 28 % capacity factor, yields 857 GWh/year—equivalent to 110 MW of continuous HPC load, or four Frontier-class supercomputers. The nodal price hedge locks Austin 4C compute clusters below $35 MWh for a decade, undercutting ERCOT peak by 60 % and freeing OPEX for A100-to-H100 refresh cycles.

How Soon Before Every New Cluster Ships With Its Own Battery?

Short-term: 2026 tenders for Frankfurt, Hyderabad and Quincy already spec 2–4 h BESS co-location. Mid-term: EU taxonomy debt now prices 40 bp cheaper for solar-plus-storage data halls, pushing CapEx below €4 M per MW IT. Long-term: wave-energy converters (Ocean Harvesting, 250 kW prototype) and biomass-to-jet CHP could add 8 % diversified reserve margin for coastal exascale sites, but only after 2030 electrolyzer scale-up drops green hydrogen to <$2 kg.

Action for operators: write PPAs at ≥1.3 × nameplate IT load, mandate grid-forming batteries ≥2 h, and insist on district-heat reuse clauses—Microsoft’s Dublin campus already pumps 200 GWh/year into city pipes, cutting CO₂e 82 %. Ignore the checklist and tomorrow’s LINPACK will benchmark your carbon bill alongside FLOPS.

In Other News

- New Quantum Satellite Alignment Tech Achieves 99.9% Precision in 10 Minutes

- Microsoft Integrates WebP Wallpaper Support into Windows 11 Release Preview, Enhancing Desktop Efficiency

Comments ()