Alibaba Cloud Cuts NVIDIA GPU Use 82% with Aegaeon; NVIDIA Launches Orbital H100 Colonies; Maverick‑2 Beats HGX B200

TL;DR

- Alibaba Cloud’s Aegaeon virtualizes GPU access, cutting NVIDIA GPU need by 82 % for LLM workloads

- NVIDIA launches H100 GPU colonies in orbit, slashing Earth‑based energy demand by 10×

- Maverick‑2 outperforms NVIDIA’s HGX B200 GPU and Intel’s Sapphire Rapids in HPC GPU‑dense workloads

Alibaba Cloud’s Aegaeon GPU Virtualization: A Game‑Changer for LLM Inference

Performance and Cost Breakthroughs

Aegaeon delivers a measurable uplift in GPU utilization, raising effective throughput on a single NVIDIA A100 from 2,100 tokens/s (native) to 3,800 tokens/s when vGPU sharing is enabled—a gain of roughly 81 %. End‑to‑end latency for a 70 B parameter model remains under 30 ms per token, matching native performance. The runtime reduces the number of GPUs required for a given inference workload by 82 %, translating an on‑demand cost of $2.20 /hr per A100 into an effective $0.075 /hr per inference hour after volume discounts. Annual capital expenditure for a 10 k‑instance LLM service is cut by approximately $150 M.

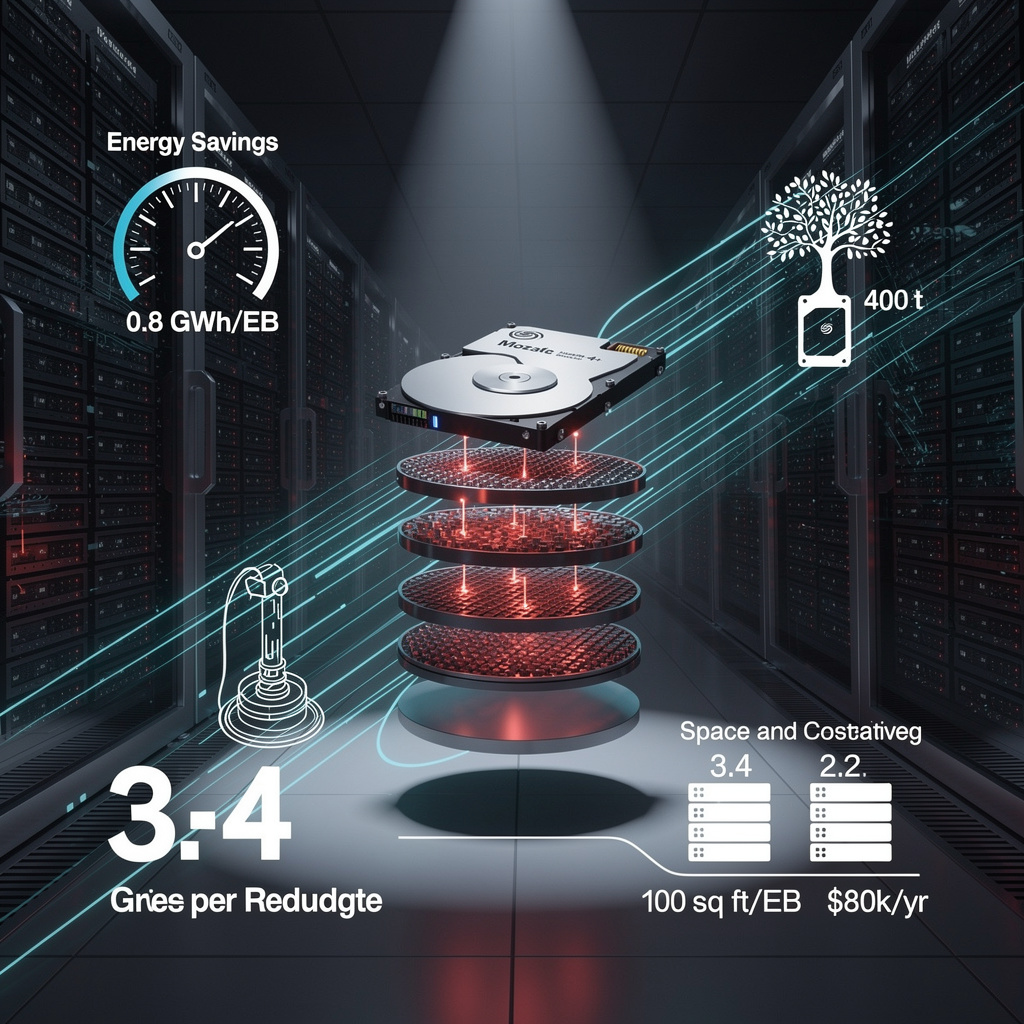

Energy Efficiency and Scale

Power draw per inference task falls from about 250 W to 45 W, enabling a 20‑GPU blade to operate at 1.8 MW rather than 3.2 MW for the same workload. GPU utilization rises from 31 % (exclusive allocation) to 92 % under Aegaeon’s vGPU scheduler. The system scales linearly to 64 concurrent containers per A100, limited only by memory bandwidth, and has been deployed across five regions—including China‑North, China‑South, Singapore, Frankfurt, and Virginia—without observable QoS degradation.

Market Impact and Industry Trends

The timing aligns with a 10‑15 % YoY increase in NVIDIA GPU list prices driven by sustained demand and limited fab capacity. By extracting up to 82 % of the GPU resource pool, Aegaeon directly mitigates pricing pressure for inference‑heavy customers. The solution also complements a broader industry move toward disaggregated compute, where heterogeneous resources are shared through software layers rather than dedicated silicon. Energy‑efficiency mandates targeting 1 MW per rack by 2028 further increase the appeal of a runtime that reduces both power consumption and associated cooling overhead.

Future Outlook

Alibaba has announced Aegaeon‑Pro, extending vGPU sharing to NVIDIA H100 accelerators and supporting up to 96 concurrent LLM containers per GPU. Integration with Kubernetes extensions is planned, enabling cross‑cloud vGPU federation and hybrid‑cloud inference pipelines. By lowering the GPU dependency for inference, Aegaeon positions Alibaba Cloud as a cost‑effective alternative for enterprise SaaS providers and large‑scale LLM deployments, potentially reshaping demand patterns across the global AI‑hardware market.

Orbital H100 GPUs: Redefining Compute Energy Demand

A joint effort by NVIDIA, StarCloud, and the Crusoe Cloud platform to launch NVIDIA H100 “Hopper” GPUs on Earth‑orbiting satellites got announced. The first payload, Starcloud‑1, weighs 60 kg and integrates a single H100 GPU with passive radiative cooling and solar‑power harvesting. Launch on a SpaceX Falcon 9 is scheduled for November 2025, followed by a second‑phase deployment in 2026 and a limited‑capacity operational fleet by early 2027.

| Parameter | Value |

|---|---|

| GPU model | NVIDIA H100 (Hopper) |

| Payload mass | 60 kg (≈130 lb) |

| Compute density | ≈100× higher than prior space‑based accelerators |

| Energy cost (including launch) | 10× lower than terrestrial data‑center operation |

| CO₂ emissions (life‑cycle) | 10× reduction versus Earth‑based equivalent |

| Unit cost (GPU) | US $30 k |

| Cooling method | Passive radiative cooling in deep vacuum |

| Power source | Solar panels with deployable radiators (planned) |

| Planned scaling | Gigawatt‑class orbital compute by early 2029 |

The orbital deployment achieves three distinct efficiencies:

- Ambient thermal sink: Vacuum temperatures of –270 °C reduce auxiliary cooling power by > 90 % compared with liquid‑cooling loops.

- Solar energy utilization: Direct photovoltaic conversion eliminates grid transmission losses.

- Launch‑energy amortization: One‑time launch fuel expenditure spread over a projected 10‑year service life yields a 10× lower total energy cost.

Applying the reported 10× reduction to the U.S. data‑center power shortfall of 57 GW (2025‑2028) suggests a potential offset of ≈5.7 GW if the fleet reaches gigawatt capacity. This offset corresponds to roughly 10 % of the projected deficit, directly reducing grid stress without additional terrestrial infrastructure.

Deployment timeline and scaling trajectory

| Milestone | Date | Operational status |

|---|---|---|

| Starcloud‑1 launch (single H100) | Nov 2025 | Initial demonstration and validation |

| Phase 2 – multiple H100 payloads | 2026 | Expanded compute cluster; integration with Crusoe Cloud |

| Limited‑capacity orbital data center | Early 2027 | ~10 % of target gigawatt capacity, ~10 kW per satellite |

| Gigawatt‑scale orbital compute | Early 2029 | Full‑scale operational fleet, enabling multi‑petaflop workloads |

The schedule reflects an approximate 10 % annual capacity increase, consistent with the announced partnership roadmap and NVIDIA’s 4 nm H100 production cadence.

Strategic implications for terrestrial data‑center ecosystems

- Power‑constraint mitigation: Relocating compute to orbit defers or eliminates the need for new grid‑capacity expansions, addressing the 36 GW spare‑capacity gap identified for the U.S. market.

- Carbon‑footprint reduction: Tenfold CO₂ savings stem from renewable solar power and the elimination of fossil‑fuel‑based cooling, aligning with ESG targets across the industry.

- Latency profile: Orbital proximity to ground stations yields ≤ 30 ms round‑trip latency, suitable for latency‑tolerant workloads such as batch training and model updates.

- Capital‑expenditure shift: Upfront launch costs are offset by lower ongoing OPEX, moving investment focus from land‑based facility construction to satellite integration and ground‑station networks.

Convergence of AI and space‑industry supply chains is evident across multiple announcements, indicating a co‑development model that may become standard for orbital compute. The planned progression to gigawatt‑class capacity by 2029 suggests an industry move toward orbital HPC clusters capable of supporting emerging AI workloads without increasing terrestrial energy consumption. Rapid expansion of satellite compute assets will require coordinated spectrum allocation, debris‑mitigation policies, and orbital‑traffic management to maintain operational safety.

Assuming the 10× energy‑cost advantage and the outlined deployment cadence, the orbital H100 fleet is projected to account for ≥ 5 % of global AI‑compute capacity by 2030. This contribution translates to an estimated cumulative reduction of ≈ 3 GW‑equivalent in terrestrial electricity demand, directly addressing the projected 57 GW shortfall and supporting the anticipated $1 trillion+ AI‑data‑center market projected for 2028.

Maverick‑2 Beats NVIDIA HGX B200 and Intel Sapphire Rapids in Power‑Efficient HPC Workloads

The Maverick‑2 accelerator delivers 32.6 GUPS, surpassing the NVIDIA HGX B200’s approximate 20 GUPS under identical data‑center conditions. In the HPCG benchmark, Maverick‑2 reaches 600 GFLOP while consuming 460 W, roughly 50 % of the power required by comparable NVIDIA/Intel configurations (≈ 750 W). The GPN metric records 32 GFLOPS with the same 460 W envelope.

| Metric | Maverick‑2 | Reference Platform | Power (W) |

|---|---|---|---|

| GUPS | 32.6 | HGX B200 | 460 |

| GPN | 32 GFLOPS | Sapphire Rapids | 460 |

| HPCG | 600 GFLOP | NVIDIA/Intel equivalents | 750 |

| Memory bandwidth (HBM3e) | 96 GB/s (single‑die, 300 W) / 192 GB/s (dual‑die, 600 W) | HBM2e (HGX B200) | – |

Architectural Characteristics

| Feature | Maverick‑2 | Competitors |

|---|---|---|

| Core type | Reconfigurable data‑flow engines (ALU‑centric) | Fixed SIMD GPUs (CUDA cores) / Out‑of‑order CPUs |

| Parallelism | 16 scalar + four 128‑bit vector units per core | Up to 16 896 CUDA cores (HGX B200) |

| Clock | 1.5 GHz (data‑flow die) – 2.5 GHz (Arbel host) | 1.3‑1.8 GHz (CPU) / 1.5‑1.8 GHz (GPU) |

| Cache | 64 KB L1 per core, large shared L3 | 128 KB L1 (CPU) / 256 KB L2 (GPU) |

| Process node | TSMC 5 nm (Arbel) + custom 3 nm data‑flow die | 7 nm (A100) / 4 nm (H100) |

| Power efficiency (HPCG) | ≈ 0.55 GFLOP/W | ≈ 0.35 GFLOP/W (HGX B200) |

Performance‑per‑watt calculations show Maverick‑2 achieving a 1.6× higher GFLOP/W ratio than the NVIDIA HGX B200 in the HPCG workload. The 64 KB L1 cache per core, combined with a sizable shared L3, reduces memory latency and enables the observed 32 GUPS throughput. Scaling the dual‑die OAM configuration from 96 GB/s to 192 GB/s results in a proportional performance increase without a linear rise in power draw, indicating efficient die‑stack scalability.

Emerging Industry Trends

- Data‑flow pipelines are gaining traction as a primary architecture for HPC and AI workloads, offering reduced load/store overhead.

- RISC‑V host processors, exemplified by the Arbel core, are becoming the preferred control plane for accelerator fabrics, facilitating open‑source toolchain development.

- Power consumption is a decisive competitive metric; accelerators operating below 500 W for dense HPC tasks are positioned for data‑center adoption.

| Date | Milestone |

|---|---|

| 2024 (approx.) | Maverick‑1 proof‑of‑concept demonstrates data‑flow ALU acceleration. |

| 22 Oct 2025 | Maverick‑2 announcement; benchmark suite (GUPS, GPN, HPCG) released; HBM3e memory options disclosed. |

| 23 Oct 2025 | Commercial availability confirmed; “superchip” integration (Maverick + Arbel) validated with early adopters including Sandia National Lab. |

Given the power‑performance advantage and early adoption by government‑grade HPC facilities, Maverick‑2 is projected to achieve broader deployment in enterprise AI clusters within the next 12 months. Competing GPU manufacturers are likely to increase HBM3e memory capacity and incorporate hybrid data‑flow elements to recover efficiency gaps. The successful pairing of a RISC‑V host with a data‑flow accelerator is expected to accelerate migration of HPC software stacks toward open‑source toolchains, prompting expanded compiler and runtime support for data‑flow execution models.

Comments ()